One-Transistor FeFET memory

- Ferroelectric Fet Memory Window

- Fefet Nvm 2020

- Mengwei Si

- Negative Capacitance Ferroelectric Fet

- Ferroelectric Fets-based Nonvolatile Logic-in-memory Circuits

Integrated Ferroelectrics Citations: 790 Integrated Ferroelectrics provides an international, interdisciplinary forum for electronic engineers and physicists as well as process and systems. USB Type-C adds a new reversible connector, support for 100-W USB Power Delivery, 10-Gbps SuperSpeed+ USB 3.1, and DisplayPort or PCIe signals in a single cable.

- Ferroelectric FET is a new type of memory. Field Programmable Gate Array (FPGA) Reprogrammable logic device. The use of metal fill to improve planarity and to.

- FB DRAM—floating body DRAM FeFET—ferroelectric FET Multiple T—multiple transistor SONOS—silicon/. Remanent polarization on a ferroelectric capacitor.

- A family of compact non-volatile flip-flops with ferroelectric FET AA Saki, SH Lin, M Alam, SK Thirumala, SK Gupta, S Ghosh IEEE Transactions on Circuits and Systems I: Regular Papers 66 (11), 4219-4229, 2019.

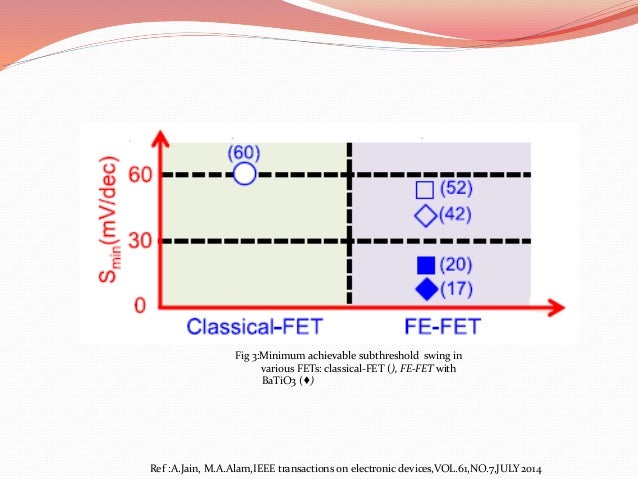

Due to the fact that hafnium oxide represents the state-of-the-art gate insulator for literally all high-k metal-gate (HKMG) process nodes, the inherent advantage of ferroelectric HfO2 is immediately revealed: You can take a standard HKMG transistor, modify its gate insulator to become ferroelectric and end up with the industry’s first nonvolatile HKMG transistor, the FeFET (see Fig. 3).

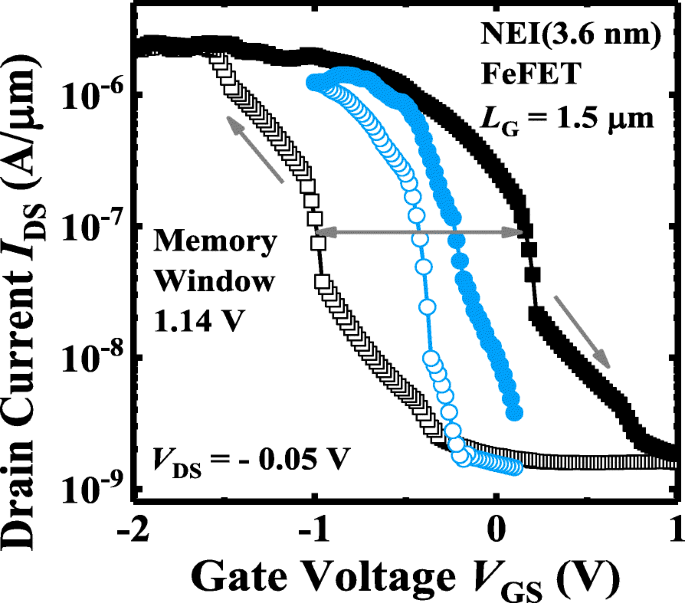

The FeFET shows nonvolatile characteristics due to the fact that the two stable, remanent polarization states of the now ferroelectric gate insulator modify the threshold voltage even when supply voltage is removed. Accordingly, the binary states are encoded in the threshold voltage of the transistor (see Fig. 4). Even though similar to Flash in its operation, the FeFET provides orders of magnitude improvement in almost any performance attribute (see also “Major differentiation to competition”). The FeFET for HKMG is introduced in order to become what Flash is today for Poly / SiON technology nodes: The overall leader in nonvolatile memories.

Fig. 3: Way of deriving nonvolatile FeFETs from standard HKMG logic transistors (exemplified for a Fully-Depleted-Silicon-On-Insulator (FDSOI) technology platform)

Fig. 4: Illustration of FeFET (n-type) functionality. When the ferroelectric polarization is pointing downwards (left) electrons invert the channel region permanently bringing the FeFET into the 'ON'-state. If the polarization is pointing upwards (middle), permanent accumulation is created and the FeFET is in the 'OFF'-state. Accordingly, binary states are encoded in the threshold voltage of the transistor (right).

Mar/2021: The paper titled 'Computing in Memory using Ferroelectrics: From Single- to Multi-Input Logic', by Q. Huang, D. Reis, C. Li, M. Niemier, X. Sharon Hu, M. Imani, X. Yin, and C. Zhuo was accepted to the Special Issue on Near-Memory and In-Memory Processing, IEEE Design & Test of Computers, 2021.

Ferroelectric Fet Memory Window

Fev/2021: The special session paper titled 'Exploiting FeFETs via cross-layer designs from In-memory Computing Circuits to Meta-Learning Applications', by D. Reis, A.F. Laguna, M. Niemier, and X. Sharon Hu was presented in the Design and Automation in Europe (DATE) conference, 2021.

Dec/2020: The paper titled 'Two-dimensional circuits with reconfigurable polarities for secure circuits', by P. Wu, D. Reis, X. Sharon Hu, and J. Appenzellerwas published in Nature Electronics (Dec 2020). https://doi.org/10.1038/s41928-020-00511-7

Sep/2020: The paper titled 'Algorithmic Acceleration of B/FV-like Somewhat Homomorphic Encryption for Compute-Enabled RAM', by J. Takeshita, D. Reis,T. Gong, M. Niemier, X. Sharon Hu, and T. Jung was accepted for publication in the Selected Cryptography Areas (SAC) 2021.

Sep/2020: The paper titled 'Attention-in-Memory for Few-Shot Learning with Configurable Ferroelectric FET Arrays', by D. Reis, A. Laguna, M. Niemier, and X. Sharon Hu was accepted for publication in the 26th Asia and South Pacific Design Automation Conference (ASP-DAC) 2021.

Ago/2020: The paper titled 'Computing-in-Memory for Performance and Energy Efficient Homomorphic Encryption', by D. Reis, J. Takeshita, T. Jung, M. Niemier, and X. Sharon Hu was accepted for publication in the IEEE Transactions on Very Large Scale Integration (VLSI) Systems.

Jul/2020: Presented a summary of my PhD work, 'Circuits and Architectures forA Fast and Energy Efficient Computing-in-Memory Architecture for Few-Shot Learning Applications,' by D. Reis, A. Laguna, M. Niemier, and X. Sharon Hu is accepted for publication in Design and Automation in Europe (DATE) 2020.

Oct/2019: The paper titled 'The Impact of Ferroelectric FETs on Digital and Analog Circuits and Architectures,' by X. Chen, S. Datta, X.S. Hu, ... D. Reis et al is accepted for publication in the IEEE Design and Test journal.

Sep/2019: Gave a talk titled 'A Computing-in-Memory Engine for Searching on Homomorphically Encrypted Data' at 2019 Arm Research Summit, Austin, TX, September, 2019.

Jul/2019: The paper titled 'Design and Analysis of an Ultra-Dense, Low-Leakage, and Fast FeFET-Based Random Access Memory', by D. Reis, et al was published in the IEEE Journal on Exploratory Solid-State Computational Devices and Circuits.

Jul/2019: The paper titled 'A Computing-in-Memory Engine for Searching on Homomorphically Encrypted Data', by D. Reis, M. Niemier, and X. Sharon Hu was published in the IEEE Journal on Exploratory Solid-State Computational Devices and Circuits.

Jul/2019: The invited paper titled 'Ferroelectric FET based TCAM Designs for Energy Efficient Computing', by X. Yin, D. Reis, Michael Niemier, and X. Sharon Hu was published in Proceedings of ISVLSI 2019.

Jul/2019: The invited paper titled 'Accelerating Deep Neural Networks in Processing-in-Memory Platforms: Analog or Digital Approach?', by S. Angizi, Z. He, D. Reis, X. Sharon Hu, W. Tsai, S. Jay Lin, and D. Fan was published in Proceedings of ISVLSI 2019.

May/2019: The invited paper titled 'Ferroelectric FET Based In-Memory Computing for Few-Shot Learning', by A. Laguna, X. Yin, D. Reis, M. Niemier and X.S. Hu was published at Proceedings of GLSVLI 2019.

Jan/2019: I was awarded as one of the recipients of the Cadence Women in Technology (WIT) Scholarship 2019.

Dec/2018: The paper titled 'An Ultra-dense 2FeFET TCAM Design based on a Multi-Domain FeFET Model ', by X. Yin, K. Ni, D. Reis, S. Datta, M. Niemier and X. S. Hu was accepted for publication in IEEE Transactions on Circuits and Systems II: Express Briefs (TCAS-II).

Sep/2018: Gave a presentation titled: 'FeFET-CiM: A Computing in Memory Solution to Reduce the Overheads Associated with Data Transfer' at TECHCON 2018 (Austin, TX).

Aug/2018: The poster titled 'Computing in memory with FeFETs', by D. Reis, M. Niemier and X.S. Hu was presented at ASCENT Review 2018 (Notre Dame, IN).

Jul/2018: The paper titled 'Computing in memory with FeFETs', by D. Reis, M. Niemier and X.S. Hu received the Best Paper Award at ISLPED 2018.

Jun/2018: The paper titled 'Computing in memory with FeFETs', by D. Reis, M. Niemier and X.S. Hu was accepted for oral presentation at ISLPED 2018 (Seattle, WA).

Apr/2018: Attended CRA-W Grad Cohort Workshop for Women (San Francisco, CA). It was a great opportunity to get some valuable advice from expert women in the field of Computing and introduce a bit of my work to others.

Fefet Nvm 2020

Aug/2017: The poster titled 'FeFET Circuits and Memory Architectures for Security Applications', by D. Reis, X. Chen, X. Yin, M. Niemier and X. S. Hu was presented at LEAST Review 2017 (Notre Dame, IN).

Mengwei Si

Apr/2017: The poster titled 'Exploiting non-volatility and low leakage power of Ferroelectric FETs for Hardware Security', by D. Reis, X. Chen, X. Yin, M. Niemier and X. S. Hu was presented at GCASR 2017 (Chicago, IL).

Negative Capacitance Ferroelectric Fet

Aug/2016: Joined University of Notre Dame as a PhD Student.

Ferroelectric Fets-based Nonvolatile Logic-in-memory Circuits

Feb/2016: Defended my MSc Thesis at Federal University of Minas Gerais (Brazil).